Hi friends.

I think i should give more detailed information.

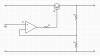

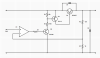

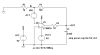

What I need is to uso a PIC microcontroller, so using 2 push-buttons, I can increase / decrease the voltage level from 0VDC to 60VDC. The PIC output range is 0-5VDC, so I need an interface to convert this signal to 0-60VDC.

Current output needed 2.5 or 3A. Load is a magnet, with the following voltage/current measured:

40V - 2.08A

34.8V - 1.85A

30.3V - 1.26A

24.5V - 0.69A

18.4V - 0.12A

17V - 0.01A

The idea is to replace actual boards to get 50 or 60VDC in order to achieve a stronger magnetic force.

Thanks!

Best regards.

I think i should give more detailed information.

What I need is to uso a PIC microcontroller, so using 2 push-buttons, I can increase / decrease the voltage level from 0VDC to 60VDC. The PIC output range is 0-5VDC, so I need an interface to convert this signal to 0-60VDC.

Current output needed 2.5 or 3A. Load is a magnet, with the following voltage/current measured:

40V - 2.08A

34.8V - 1.85A

30.3V - 1.26A

24.5V - 0.69A

18.4V - 0.12A

17V - 0.01A

The idea is to replace actual boards to get 50 or 60VDC in order to achieve a stronger magnetic force.

Thanks!

Best regards.