-

Categories

-

Platforms

-

Content

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Scroll to continue with content

barathbushan

- Sep 26, 2009

- 223

- Joined

- Sep 26, 2009

- Messages

- 223

hi,

the circuit that you have provide contains a transmission gate followed by an inverter , 4 units are cascaded .

1) the reason for using transmission gate is to just to pass the logic , for 5 volts

logic ,

(1) when logic high ,the load capacitor at pmos charges full to 5v but the nmos

charges only upto 3.5 volts resulting in logic error at certain times

(2) when logic low ,the load capacitor at nmos discharges fully to 0v but the pmos

discharges only upto 1.5 volts resulting in logic error

(3)hence there is no perfect logic 0 (0 v) or perfect logic 1 (5 v) , hence

transmission gates are used to correct this error

2)The next part of the circuit is a nmos and pmos(bubble at the gate missing) transistor connected end to end to form a cmos inverter , which inverts the logic provided at its inputs .

3)regarding your doubt about the non-overlapping clock or two phase clock ,

(1)

(2) as you see in the above diagram the clocks are connected to the gates of the

pmos and nmos transistor , which are connected in parallel .

(3)remember the bubble at the gate of pmos means any input given at its gate is

inverted

(4)so if the clock is in its ON phase , the pmos is turned off

(5) now consider giving an overlapping clock , which is same phase clock , at the

ON time of the clock , nmos is ON but pmos is OFF as mentioned earlier

which means for a given single phase clock only either nmos or pmos is turned

at a time

(6) if you give a two phase clock , then if one clock is HIGH the nmos is on , and

the other clock must be low (since two phase) , then the pmos is HIGH

CONCLUSION:for a two phase clock the pmos and nmos can be turned on or

off simultaneously thus passing perfect logic zero or logic 1 perfectly.

4)overall explanation of the above circuit

(1) when you clock the circuit , and provite data at the transmission gate , it is passed to the inverter which in inverted , after another clock the inverted data of previous stage

is inverted again , this process repeats for every clock

(2) after 4 clocks the data you had given at the first transmission gate , is finally obtained at the last inverter

(3)the above circuit is called a shift register , it is called so because it shifts the data provided for every clock

i hope i have provided some help to you

the circuit that you have provide contains a transmission gate followed by an inverter , 4 units are cascaded .

1) the reason for using transmission gate is to just to pass the logic , for 5 volts

logic ,

(1) when logic high ,the load capacitor at pmos charges full to 5v but the nmos

charges only upto 3.5 volts resulting in logic error at certain times

(2) when logic low ,the load capacitor at nmos discharges fully to 0v but the pmos

discharges only upto 1.5 volts resulting in logic error

(3)hence there is no perfect logic 0 (0 v) or perfect logic 1 (5 v) , hence

transmission gates are used to correct this error

2)The next part of the circuit is a nmos and pmos(bubble at the gate missing) transistor connected end to end to form a cmos inverter , which inverts the logic provided at its inputs .

3)regarding your doubt about the non-overlapping clock or two phase clock ,

(1)

(2) as you see in the above diagram the clocks are connected to the gates of the

pmos and nmos transistor , which are connected in parallel .

(3)remember the bubble at the gate of pmos means any input given at its gate is

inverted

(4)so if the clock is in its ON phase , the pmos is turned off

(5) now consider giving an overlapping clock , which is same phase clock , at the

ON time of the clock , nmos is ON but pmos is OFF as mentioned earlier

which means for a given single phase clock only either nmos or pmos is turned

at a time

(6) if you give a two phase clock , then if one clock is HIGH the nmos is on , and

the other clock must be low (since two phase) , then the pmos is HIGH

CONCLUSION:for a two phase clock the pmos and nmos can be turned on or

off simultaneously thus passing perfect logic zero or logic 1 perfectly.

4)overall explanation of the above circuit

(1) when you clock the circuit , and provite data at the transmission gate , it is passed to the inverter which in inverted , after another clock the inverted data of previous stage

is inverted again , this process repeats for every clock

(2) after 4 clocks the data you had given at the first transmission gate , is finally obtained at the last inverter

(3)the above circuit is called a shift register , it is called so because it shifts the data provided for every clock

i hope i have provided some help to you

Last edited:

barathbushan

- Sep 26, 2009

- 223

- Joined

- Sep 26, 2009

- Messages

- 223

hey steve , if you dont agree with me , please tell me where i have gone wrong , so that i can correct myself . oh yes i should have read the note , before posting the whole answer

Barathbushan,thank you four your explaination.

I have a few questions for you:

First I agree with your explaination why are used cmos transmission gates in this circuit.

I need to prove why this circuit can't work with overlapping clocks.

You said that with overlapping clocks in this circuit only nmos transistors are conducting and that is the reason why this circuit can't work as dynamic shift register?

I don't understand that because that's not prove.

At the output of the second inverter when I simulated this circuit I get smaller voltage

then Vdd(Vdd=5v).I get 2.5V,and there is I have problem when I used overlapping clocks.

I don't know why is this happening.

Looking at the first inverter input, the inverter’s input will be whatever is at ''Vin'' when

Phi = 1. However, when Phi1 = 0, there is no logic level since the CMOS switch will be off. In a real transistor there will be parasitic capacitance that maintains charge and keeps the logic level at what it was when the CMOS switch was on.

I have a few questions for you:

First I agree with your explaination why are used cmos transmission gates in this circuit.

I need to prove why this circuit can't work with overlapping clocks.

You said that with overlapping clocks in this circuit only nmos transistors are conducting and that is the reason why this circuit can't work as dynamic shift register?

I don't understand that because that's not prove.

At the output of the second inverter when I simulated this circuit I get smaller voltage

then Vdd(Vdd=5v).I get 2.5V,and there is I have problem when I used overlapping clocks.

I don't know why is this happening.

Looking at the first inverter input, the inverter’s input will be whatever is at ''Vin'' when

Phi = 1. However, when Phi1 = 0, there is no logic level since the CMOS switch will be off. In a real transistor there will be parasitic capacitance that maintains charge and keeps the logic level at what it was when the CMOS switch was on.

Last edited:

barathbushan

- Sep 26, 2009

- 223

- Joined

- Sep 26, 2009

- Messages

- 223

1) REMEMBER you would want both the nmos and cmos to be on simultaneously , so that their combined charging and discharging would correct the logical error .

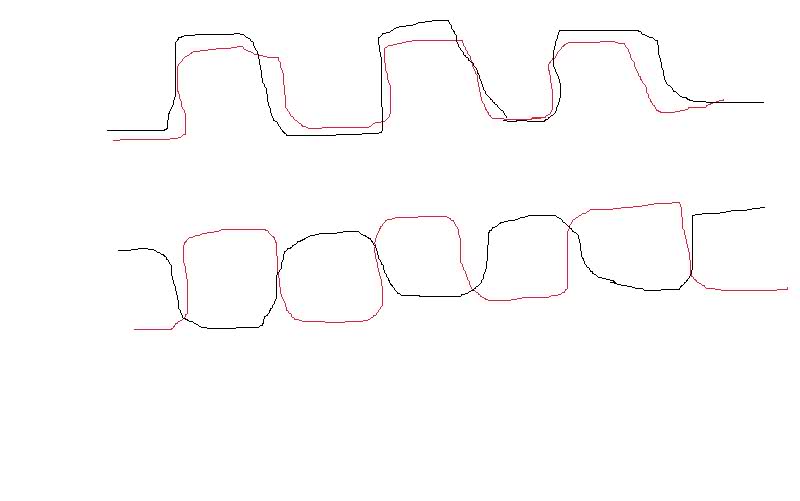

2)the "PROOF is the diagram i have provided

3)as you clearly can see , only with two phase clocks can you switch on the nmos and pmos simultaneously

4)also am surprised that you simulated this circuit , as i thought they are only

fabricated devices , if you did simulate please tell me the name of the software

2)the "PROOF is the diagram i have provided

3)as you clearly can see , only with two phase clocks can you switch on the nmos and pmos simultaneously

4)also am surprised that you simulated this circuit , as i thought they are only

fabricated devices , if you did simulate please tell me the name of the software

Last edited:

barathbushan

- Sep 26, 2009

- 223

- Joined

- Sep 26, 2009

- Messages

- 223

look carefully ,the clocks are same , the pspice simulated clock are just joined at ends

barathbushan

- Sep 26, 2009

- 223

- Joined

- Sep 26, 2009

- Messages

- 223

anyways the principle of an overlapping clock is that , both the clocks must not be in the same phase simultaneously , that is they should neither be high or low simultaneously , and my clocks follow the rule .

barathbushan

- Sep 26, 2009

- 223

- Joined

- Sep 26, 2009

- Messages

- 223

In your diagrams these are not non-overlapping clocks.

Non-overlapping clcoks means that two signals Phi1 and Phi2 are not at the

logic ''1'' at the same time.

OF COURSE MY CLOCKS ARE NOT HIGH AT THE SAME TIME

barathbushan

- Sep 26, 2009

- 223

- Joined

- Sep 26, 2009

- Messages

- 223

HERE you go , try looking at this picture

The above picture is the proof that two phase or non overlapping clocks are required to operate a tranmission gate

The above picture is the proof that two phase or non overlapping clocks are required to operate a tranmission gate

barathbushan

- Sep 26, 2009

- 223

- Joined

- Sep 26, 2009

- Messages

- 223

No the logical error is due to the inherent fault with using nmos and pmos transistor individually , by connecting both of them in parallel , and calling the arrangement as transmission gate , we eliminate the error

- Joined

- Jan 21, 2010

- Messages

- 25,510

hey steve , if you dont agree with me , please tell me where i have gone wrong , so that i can correct myself . oh yes i should have read the note , before posting the whole answer

I would, except the whole point of this section is to help people with their homework, not do it for them.

You've pretty much given this person an answer they can copy down as the answer to their assignment.

Fortunately you've made some errors which means that he won't get a perfect score.

But PLEASE don't encourage people to come here to get their homework done for them.

edit: You've noticed now, and we all make mistakes.

Last edited:

Steve,

I don't think that he made my homework.

And I think that the most important thing at dynamic shift register

is that this non-overlapping clocks have non-overlapped time (which is small),

so that's the time where two CMOS switch are OFF at the same time.

Also here is needed positive and negative edges,falling edge Phi1 and rising edge Phi2.

If you relised this circuit with 'pass' transistors pmos or nmos you will get that nmos passes weak '1' and pmos passes weak '0',so whu this circuit better works with cmos transmission gates.

And THANK YOU VERY MUCH!

I don't think that he made my homework.

And I think that the most important thing at dynamic shift register

is that this non-overlapping clocks have non-overlapped time (which is small),

so that's the time where two CMOS switch are OFF at the same time.

Also here is needed positive and negative edges,falling edge Phi1 and rising edge Phi2.

If you relised this circuit with 'pass' transistors pmos or nmos you will get that nmos passes weak '1' and pmos passes weak '0',so whu this circuit better works with cmos transmission gates.

And THANK YOU VERY MUCH!

barathbushan

- Sep 26, 2009

- 223

- Joined

- Sep 26, 2009

- Messages

- 223

its the inverse of what you say andrea

barathbushan

- Sep 26, 2009

- 223

- Joined

- Sep 26, 2009

- Messages

- 223

i dont know about overlapping and non overlapping clocks , or what you are talking about , all i know is that the second clock configuration in the above diagram is used to operate the transmission gate

Similar threads

- Replies

- 3

- Views

- 1K

S

- Replies

- 1

- Views

- 1K

S

S

- Replies

- 3

- Views

- 1K

A