Why is it required to use dv/dt may be in this particular scenario.

Because V changes over time in a non-stationary, non-sinusouidal manner. It is

explained e.g. here or find another explanatio that suits you better?

Or let me trry to explain it without differential equations:

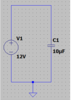

At t= 0 the capacitor is discharges, Vc = 0 V.

Thus when the input voltage jumps from 0 V to 12 V, this voltage is fully across the resistor and I = V/r applies with the resulting 120 A for a 0.1 Ω resistor, as you observed.

Now take a step in time forward: The current has charged the capacitor, thus the voltage across the capacitor starts to rise. The voltage across the resistor on the contrary is reduced since this voltage is the difference between input voltage and the voltage across the capacitor: Vr = Vin-Vc. The reduced Vr in turn leads to a reduced current: I = Vr/R = (Vin-Vc)/R.

Take another step forward in time: Again the capacitor's voltage has increased, but more slowly since the current is reduced compared to the initial condition. Apply the same reasoning as above: Rising capacitor voltage reduces the voltage across the resistor which in turn reduces the current.

This is why the current slowly but steadily decreases (exponentially) while the voltage across the capacitor increases in the same way.

When you make the time steps infinitesimally small you arrive at the differential equations.

In a real circuit there are, apart from the capacitor's ESR, other factors limiting the current:

- wiring resistance

- limited current drive capability of the voltage source (inner resistance or enforced current limiting)

These all can easily be modeled in LTSPICE either as parameters of the component (as shown in my post #4 - this is the preferred method!) or as separate components (not preferred due to the way these parasitics can be handled more effectively when entered as component parameters.