Hi Guys,

Let me start by saying I'm quite a bit out of my depth here, so this is an appeal for good books more than anything else. That said, I'm trying to build a frequency synthesizer that tunes from 30.5MHz to 32MHz with coarse and fine tuning capability (it's going to be used as an LO in a transceiver build). I opted to use the ADF4002 as the PLL IC with fine tuning provided by a AD9851 DDS module in an offset-PLL configuration shown below.

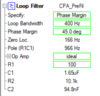

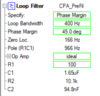

I used the Analog Devices ADISim tool to calculate the low-pass filter (LPF) and I initially opted for a 4-pole active design. This worked fine for the coarse tuning, which is provided by changing the N count in the ADF4002 with no mixer or BPF included in the loop. However, as soon as I wired up the mixer and BPF, the loop wouldn't lock and I suppose thinking about it now, that's not a surprise.

The BPF is a modified 3rd order Cheby and the mixer is a NE612. I posted a question on SE ( https://electronics.stackexchange.c...ency-for-a-mixed-signal-frequency-synthesizer ) at the time, which will provide more detail.

I've since opted for a much simpler 2-pole filter:

I'm about to try this simpler filter but I'm not entirely optimistic it will work. I've been doing some research on offset-PLL topologies and I'm struggling to find the answers I'm looking for. So, here are my (simple) questions:

If I want to model this analytically, should I be concerned about the effect of the bandpass filter and mixer (the problem is the ADISim tool has no idea they exist in the loop)?

Any recommendations for books with a strong analytical treatment of offset-PLL architectures?

Any practical recommendations on how to measure the effect of the mixer and filter in-circuit so that I can make some adjustments to a standard loop transfer function?

Let me start by saying I'm quite a bit out of my depth here, so this is an appeal for good books more than anything else. That said, I'm trying to build a frequency synthesizer that tunes from 30.5MHz to 32MHz with coarse and fine tuning capability (it's going to be used as an LO in a transceiver build). I opted to use the ADF4002 as the PLL IC with fine tuning provided by a AD9851 DDS module in an offset-PLL configuration shown below.

I used the Analog Devices ADISim tool to calculate the low-pass filter (LPF) and I initially opted for a 4-pole active design. This worked fine for the coarse tuning, which is provided by changing the N count in the ADF4002 with no mixer or BPF included in the loop. However, as soon as I wired up the mixer and BPF, the loop wouldn't lock and I suppose thinking about it now, that's not a surprise.

The BPF is a modified 3rd order Cheby and the mixer is a NE612. I posted a question on SE ( https://electronics.stackexchange.c...ency-for-a-mixed-signal-frequency-synthesizer ) at the time, which will provide more detail.

I've since opted for a much simpler 2-pole filter:

I'm about to try this simpler filter but I'm not entirely optimistic it will work. I've been doing some research on offset-PLL topologies and I'm struggling to find the answers I'm looking for. So, here are my (simple) questions:

If I want to model this analytically, should I be concerned about the effect of the bandpass filter and mixer (the problem is the ADISim tool has no idea they exist in the loop)?

Any recommendations for books with a strong analytical treatment of offset-PLL architectures?

Any practical recommendations on how to measure the effect of the mixer and filter in-circuit so that I can make some adjustments to a standard loop transfer function?