Chengjun Li

- Oct 21, 2014

- 84

- Joined

- Oct 21, 2014

- Messages

- 84

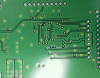

I am now working on designing an evaluation board for a capacitve read out chip since the board is no longer fabricated by the manufacture. The board is used to measure extremely small capacitance difference between external capacitors. The picture of the board is shown below.

I am not sure how the wire is routed on the highlighted area of the board.

It seems SI pin on the chip is connected to a via to the left. Then the signal goes to the bottom of the board,from there I guess it is further connected to the via under the third pin of the op amp in the highlighted area. And then connected to the hole SI to the left edge of the board. There is a wide trace as you can see, to the right the trace is isolated from and stop at the first via mentioned above, and to the left it first connects to the first two pins of the op amp and then connects to the two holes on top and bottom of the hole SI.

1. Is my description of the connection correct?

2. If I am correct, what's the purpose of the wide trace?Is it for reduce the noise from parasitic capacitance?how does it work?

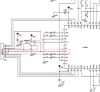

The schematic is shown below with the same region highlighted.

I am not sure how the wire is routed on the highlighted area of the board.

It seems SI pin on the chip is connected to a via to the left. Then the signal goes to the bottom of the board,from there I guess it is further connected to the via under the third pin of the op amp in the highlighted area. And then connected to the hole SI to the left edge of the board. There is a wide trace as you can see, to the right the trace is isolated from and stop at the first via mentioned above, and to the left it first connects to the first two pins of the op amp and then connects to the two holes on top and bottom of the hole SI.

1. Is my description of the connection correct?

2. If I am correct, what's the purpose of the wide trace?Is it for reduce the noise from parasitic capacitance?how does it work?

The schematic is shown below with the same region highlighted.